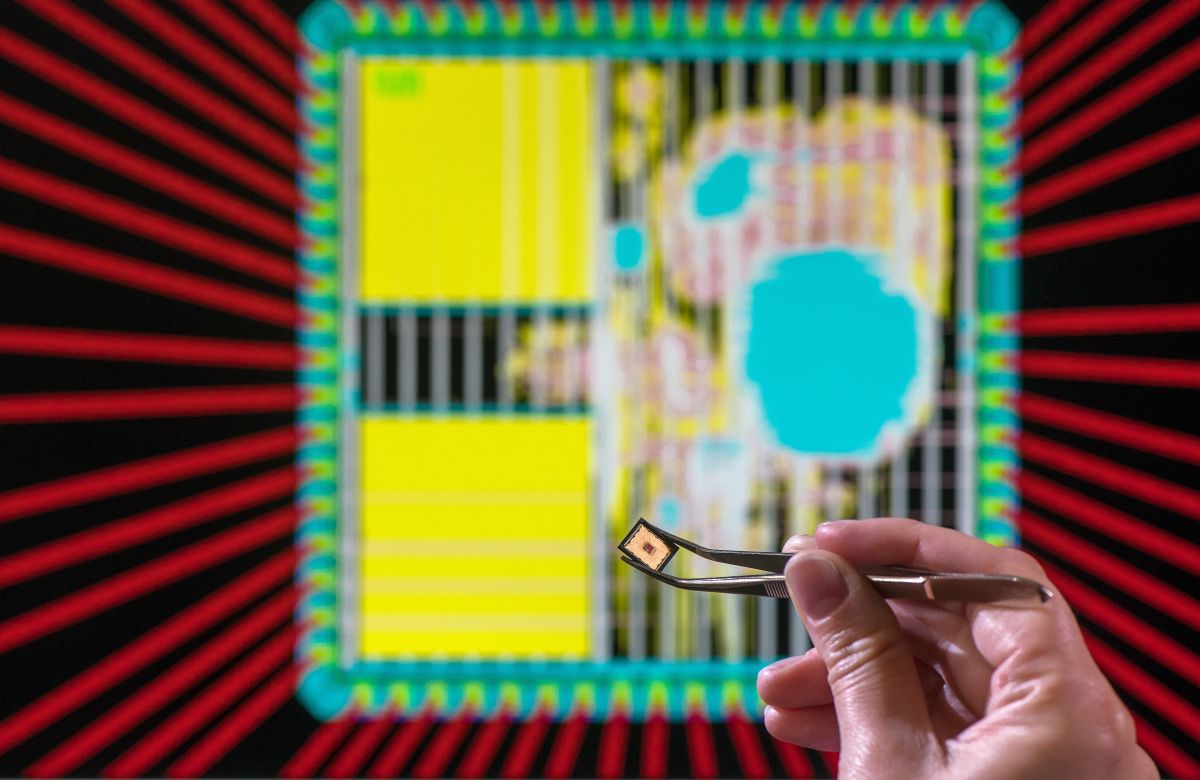

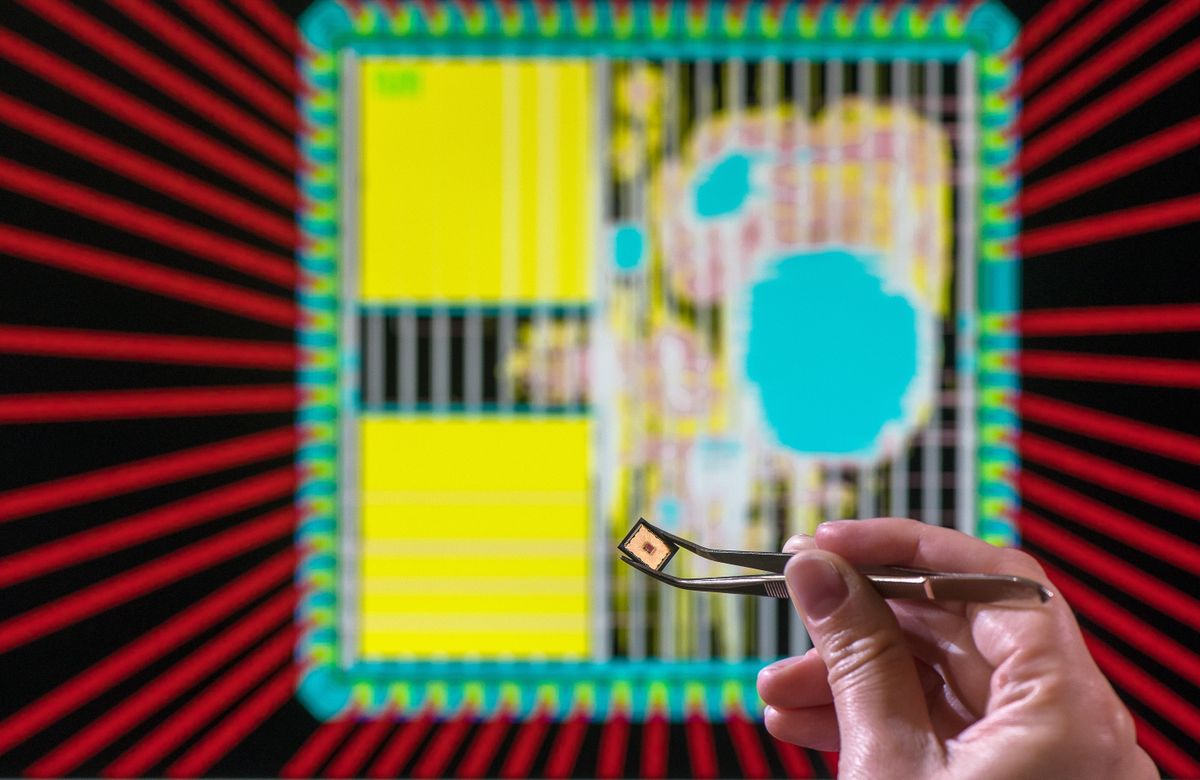

Researchers have designed a chip that incorporates four hardware trojans, which they hope to use to help them study and work out efficient strategies to nullify against such hardware-based attacks.

Designed by researchers at the Technical University of Munich (TUM), the chips are meant to efficiently implement post-quantum cryptography, in light of the fact that Quantum computers are expected to render the current encryption algorithms completely useless.

The chip, which has already been approved for production, is a milestone since it successfully manages to address the issue of the enormous processing power that the post-quantum encryption methods require.

“Ours is the first chip for post-quantum cryptography to be based entirely on a hardware/software co-design approach. As a result, it is around 10 times as fast when encrypting with Kyber, one of the most promising candidates for post-quantum cryptography, as compared to chips based entirely on software solutions. It also uses around eight times less energy and is almost as flexible,” says Georg Sigl, Professor of Security in Information Technology, who heads the team of researchers at TUM.

Hardware trojans inside

The chip is an application-specific integrated circuit (ASIC) and is a modification of an open source chip design based on the open source RISC-V standard. The design also incorporates a purpose-designed hardware accelerator.

Reasoning that hardware-based trojans could nullify the advantages of a post-quantum cryptography, the researchers also incorporated some into their chip to watch and study them in action.

“To develop protective measures, we need to think like an attacker and try to develop and conceal our own trojans. In our post-quantum chip we have therefore developed and installed four hardware trojans, each of which works in an entirely different way,” explains Sigl.

The researchers will study the chips over the next few months, before taking them apart in a complex process for research purposes. The intent here is to develop standardized processes to check that chips rolling out from the assembly line are up to spec and that their design hasn’t been tampered with by high-tech rouge agents.